Watch this demo to see how you can optimize your Quartus II designs for timing, power, or area using DSE.įaster Simulation with the ModelSim-Altera Edition Software & amp amp amp amp amp amp amp amp amp amp #160 DSE 2.0 enables faster convergence to the optimal Quartus II software settings with new exploration strategies and efficient farming of compiles to workload management software, namely LSF or Sun Grid. Quartus II software v14.1 also offers an enhanced next-generation Design Space Explorer (DSE), a simple and easy-to-use design optimization tool that explores and reports Quartus II software options that are optimal for your design. Enhanced IP IntegrationĪ new IP integration flow that is composed of a migration wizard and a centralized IP catalog simplifies the IP selection and migration to new Altera devices. The JNEye link analysis tool also performs new causality and passivity checks, and reports several new measures of noise.įor more information, visit the JNEye web page. The JNEye link analysis tool makes a significant leap with new channel analyzer capabilities that includes support for different transmission line models (e.g. See how the floating-point megafunctions can automatically target the new Arria 10 device DSP architecture with minimal user effort. This video demonstration shows the design entry (via Quartus II software megafunctions) for floating-point DSP algorithms leveraging the new hard floating-point DSP blocks in Arria 10 devices.

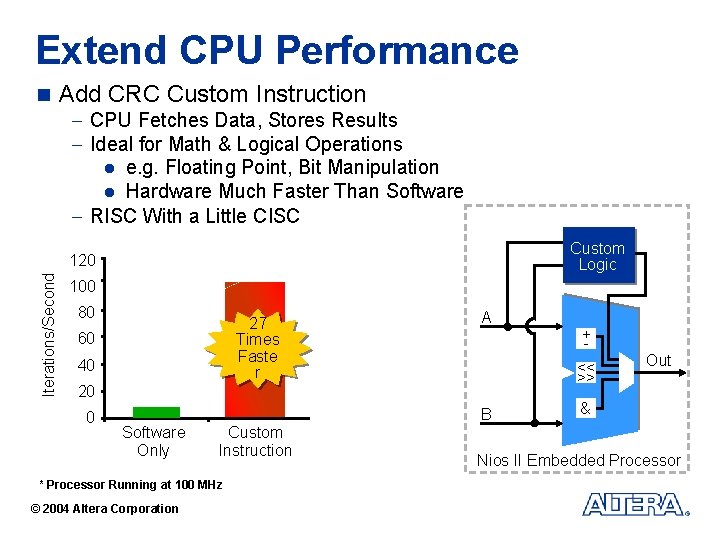

A wide range of mathematical functions support the hardened floating-point implementation (e.g.You can develop floating-point algorithms by instantiating Altera’s floating-point megafunctions and MegaCore ® functions directly from your RTL code.The compiler automatically optimizes the hardware implementation by taking advantage of the floating-point operators in the DSP blocks.The Altera SDK for OpenCL allows users to abstract away the traditional hardware FPGA development flow for a much faster and higher level software development flow.C-based design flow with the Altera ® SDK for OpenCL TM *.The updated DSP builder libraries include enhanced Math.h functions and updated design examples that support DSP blocks with hardened floating-point operators.DSP Builder enables automatic high-performance push-button HDL generation of DSP algorithms directly from the Simulink environment.Model-based design flow with DSP Builder and MathWorks Simulink.With Quartus II software v14.1, you can realize the benefits of the hardened floating-point implementation through multiple design flows that include a model-based, C-based, and RTL-based design flow: With a hardened floating-point adder and multiplier in every DSP block, Arria 10 devices deliver up to 1.5 tera floating point operations per second (TFLOPS) of performance while reducing your floating-point design resources by 80 percent compared with previous implementations. You can harness the performance and productivity advantages of hardened floating-point blocks in Arria 10 devices. Productivity Advantage Multiple Design Flows for DSP Hardened Floating-Point Blocks Power management controller reference designs.New Analog Toolkit (Beta release) for evaluating analog-to-digital converter (ADC) performance and for hardware debug.Enhanced Flash MegaWizard TM support for new modes such as configuration flash memory (CFM) and user flash memory (UFM).

0 kommentar(er)

0 kommentar(er)